1、计算机系统的组成

计算机系统由硬件和软件两部分组成

硬件,是指计算机的实体部分,由看得见摸得着的各种电子元器件组成,如主机、外设

软件,是指具有各类特殊功能的程序,通常放在计算机的主存或辅存中

软件分为系统软件和操作软件

系统软件(程序软件),用来管理整个计算机系统,监听服务,调度系统资源,包括:标准程序库、语言处理程序、操作系统、服务程序、数据库管理系统、网路软件等

应用软件(应用程序),用户根据任务需要所编制的各种程序

2、冯诺依曼机器的主要特点?

1)计算机由运算器、存储器、控制器、输入设备和输出设备五大部分组成;

2)指令和数据存储在存储器中,并可以按地址访问;

3)指令和数据均以二进制表示;

4)指令由操作码和地址码构成,操作码指明操作的性质,地址码表示操作数在存储器中的位置;

5)指令在存储器内按顺序存放,通常按自动的顺序取出执行;

6)机器以运算器为中心,I/O设备与存储器交换数据也要通过运算器。(后来以存储器为中心)

3、区分存储单元、存储字、存储字长、存储体、机器字长、存储字长

存储单元:存储一个存储字并具有特定存储地址的存储单位;

存储字:一个存储单元中存放的所有的二进制数据,按照某个地址访问某个存储单元获取的二进制数据。

存储字长:存储字中二进制数据的位数,即按照某个地址访问某个存储单元获取的二进制数据的位数;

存储体:由多个存储单元构成的存储器件。

机器字长:CPU一次能够处理的二进制数据的位数。

存储字长:按照某个地址访问某个存储单元获取的二进制数据的位数。

4、区分MAR,MDR

1)MAR:存储地址寄存器,保存需要访问的存储单元地址。反映存储单元的个数。

2)MDR:存储数据寄存器,缓存读出/写入存储单元的数据。反映存储字长。

3)存储器的最大容量由MAR寄存器的位数和MDR寄存器的位数决定

5、MAR与MDR的计算

假设MAR寄存器的位数为16位,MDR寄存器的位数为16位,存储器的最大容量是多少?

1)MAR寄存器的位数为16位,能表示的地址个数为2的16次方,为64K;

2)MDR寄存器的位数为16位,说明存储字长为16位,也即2个字节;

3)存储器的最大容量为64K * 2B = 128K Byte

总线是连接多个部件的信息传输线,是各部件共享的传输介质

{总线实际上是由许多传输线或通路组成,每条线可一位一位地传输二进制代码,一串二进制代码可在一段时间内逐一完成。若干条传输线可以同时传输若干位二进制代码。

例:16条传输线组成的总线可同时传输16位二进制代码)

机械特性:几何尺寸、形状、引脚的个数、排列顺序

电气特性:信号传递方向、有效电平范围

功能特性:总线中每根传输线的功能

时间特性:总线中的任一根线的有效时间

1)总线宽度:数据总线的根数,一般是8的倍数。是衡量计算机系统性能的重要指标;

2)总线带宽:即总线数据传输速率,总线上每秒能够传输的最大字节量。

3)时钟同步/异步:与时钟同步/不同步工作的总线

4)总线复用:一条信号线上分时传送两种信号

5)信号线数:地址总线+数据总线+控制总线

6)总线控制方式:突发工作、自动配置、仲裁方式、逻辑方式、计数方式

7)其他指标:负载能力、电源电压、总线宽度能否扩展等

总线带宽=总线宽度*时钟频率

总线带宽=总线宽度/时钟周期

例:总线宽度为32bit,时钟频率为200MHz,若总线上每5个时钟周期传送一个32bit的字,问总线带宽是多少?

解答:总线时钟频率为200MHz,

1 个时钟周期为1/200MHz=0.005μs

总线传输周期为0.005μs×5=0.025μs

由于总线的宽度为32 位=4B(字节)

故总线的数据传输率为4B/(0.025μs)=160MBps

【说明】总线宽度为32位=4字节,其中32位指的是一次能处理32个二进制,而8个二进制等于1个字节,所以32位一次能传送32/8=4B,即4个字节

若想提高数据传输率:增大数据线宽度/增加总线时钟频率

解决系统、模块、设备与总线之间不适应、不通用及不匹配的问题

ISA总线、EISA总线、VESA总线、PCI总线、AGP总线、RS-232C总线、USB总线

支持即插即用(Plug and Play):PCI、USB、EISA

2)地址总线:指出地址码,单向:由CPU发出

3)控制总线:发出控制信号,对于控制总线中的单根线,是单向的,即只能由一个部件发向另一个部件。而一组控制总线中,有输入也有输出,因此,控制总线也可以看成是双向的。

1)总线周期:完成一次总线操作的时间(总线上两个部件完成一次完整且可靠的数据传输时间)

2)分为四个阶段:申请分配阶段:申请总线

寻址阶段:发出地址及有关命令

传数阶段:进行数据交换

结束:从总线上撤除信号,让出总线

~总线判优控制(解决多个部件同时申请总线时的使用权分配问题)

常见的集中控制优先权仲裁方式:

链式查询:对电路故障最敏感

计数器定时查询:查询方式优先级设置较灵活

独立请求方式:响应速度快

~总线通信控制(解决通信双方如何获知传输开始和传输结束,以及通信双方如何协调配合)

通信控制四种方式:同步通信、异步通信、半同步通信、分离式通信

~~同步通信:总线上各个部件由统一的时钟信号控制;在总线周期中,每个时钟周期各个部件如何动作都有明确的规定。

优点:速度快,各个模块间配合简单

缺点:以总线上最慢的部件来设计公共时钟,影响总线效率。

~~异步通信:总线上各部件没有统一的时钟标准,采用应答式通信;(主模块发出请求后,一直等到从模块反馈回来应答信号之后才开始通信)

异步通信的应答方式分为:不互锁、半互锁、全互锁

波特率:单位时间内传送的二进制数据数据的位数,单位bps

比特率:单位时间内传送的有效的二进制位数,单位bps

例如:在异步串行传送系统中,字符格式为:1个起始位、8个数据位、1个校验位、2个终止位。若要求每秒传送120个字符,试求传送的波特率和比特率。

一帧包含:1+8+1+2=12位

波特率为:(1+8+1+2)*120=1440bps

比特率为:8*120=960bps

奇偶校验只能检错,不能纠错。汉明码可以纠错。

17、异步通信时规需要设置的参数

波特率、停止位(1/2/1.5)、校验位(奇校验、偶校验、无校验)

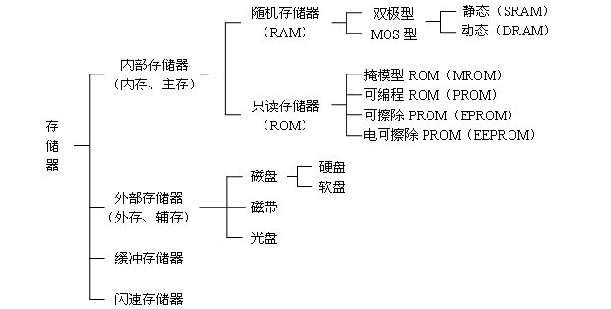

18、存储器的分类

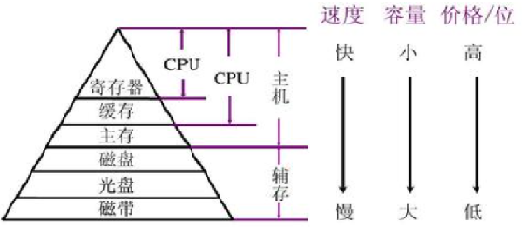

19、常见的存储系统层次结构

1)缓存-主存层次:用来缓解CPU和主存速度不匹配的问题,由硬件来完成,对所有的程序员完全透明。

2)主存-辅存层次:用来解决主存容量不够的问题,由操作系统和硬件共同完成,对应用程序设计者透明,对系统程序设计者不透明。

20、主存的三个主要技术指标

存储容量、存取速度和存储带宽

21、在CPU和内存之间引入cache的原因

1)避免cpu空等I/O访存;

2)缓解CPU和主存速度不匹配的问题。

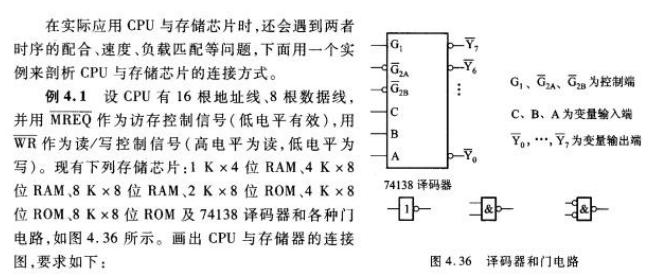

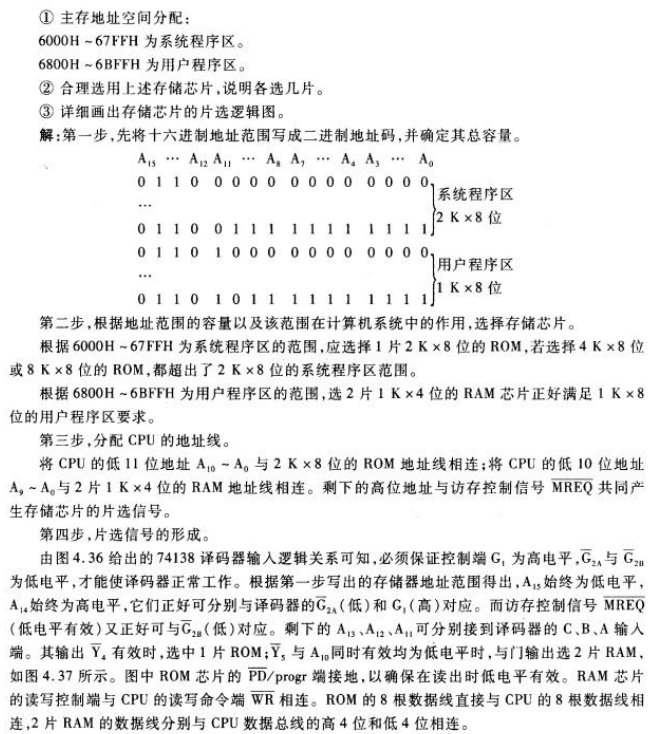

22、存储器与CPU的连接--必考大题

23、存储器流水线工作

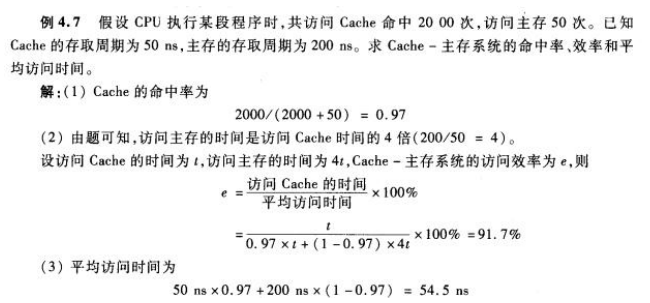

24、命中率、访问效率、平均访存时间问题

命中:主存与缓存建立关系

未命中:主存与缓存未建立关系,缓冲中没有可要的数据

25、Cache的组成

Cache存储体、地址映射变换机构、Cache替换机构、Cache的读写操作

26、Cache写操作的两种方式

写直达法:数据既写入Cache又写入主存

写回法:数据只写入Cache而不写入主存,当Cache中数据被替换出去之后才写入主存

27、地址映射(由主存地址映射到Cache地址)

地址映射方式:直接映射、全相联映射、组相联映射

相关计算:

28、中断的概念

计算机在执行程序过程中,当出现异常清空或特殊请求时,计算机停止现行程序的运行,转去处理这些异常清空或特殊请求,处理结束后,再返回现行程序的间断处,继续执行原程序

29、中断服务程序的基本流程

1)保护现场

2)中断服务

3)恢复现场

4)中断返回

30、I/O接口

I/O接口:主机与I/O设备之间设置的一个硬件电路及其相应的软件控制

端口:I/O接口内CPU能够访问的寄存器

I/O接口的功能:选址、传送命令、传送数据、反应I/O设备工作状态

I/O接口的类型:并行接口、串行接口(数据传送方式)

程序型接口(程序控制接口、程序中断接口)、DMA型接口(数据传送的控制方式)

来源:https://www.cnblogs.com/yiduoyun0826/p/12168791.html