亚稳态是由于违背触发器的建立保持时间产生的,一般来说,触发器都会在一个或者两个时钟周期内从亚稳态返回稳态。

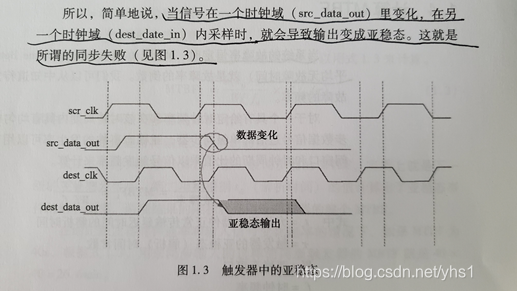

亚稳态窗口(Metastability Window)具有特定的时间长度,这段时间内输入信号和时钟都应该保持不变,如果它们发生变化,输出可能变成亚稳态,建立时间和保持时间共同决定了亚稳态窗口的宽度。

亚稳态出现的条件通常有

- 输入信号是异步信号。

- 时钟偏移/摆动(上升/下降时间)高于容限值。

- 信号跨时钟域(包括跨同频不同相的时钟域)。

- 组合逻辑延时使数据在触发器的亚稳态窗口发生变化。

- 系统时钟频率过高。

关于亚稳态的建议

在两个异步系统的交界处亚稳态是不可避免的,但使用以下方法可以减少亚稳态的发生概率

- 采用同步器。

- 避免使用dV/dt低的输入信号。

- 采用相应更快的触发器(缩短亚稳态窗口)。

- 减少组合逻辑的延时。

- 降低时钟频率。

亚稳态监测电路

同步器

模式A (T async_in > T clk)

模式B (T async_in < T clk)

以上内容摘自 The Art of Hardware Architecture.

来源:https://blog.csdn.net/yhs18200259681/article/details/98785036