FPGA计数器学习

通过led每500ms翻转一次,来显示我们的代码执行情况。

对系统时钟进行计数来实现。我们设置系统时钟为50MHz,对应的周期为20ns。

让计数器记满500ms,则需要计数次数为500 000 000/20=25 000 000

可以看出25 000 000需要25位

首先创建工程文档

然后新建counter.v文件

module counter(Clk50M,Rst_n,led);//_n表示低电平有效

input Clk50M;//系统时钟 50M

input Rst_n;//全局复位,低电平复位

output reg led;

reg [24:0]cnt;

//用always块设计一下时序逻辑

//控制计数

always@(posedge Clk50M or negedge Rst_n)//时序逻辑里比较常见的写法,将时钟上升沿作为敏感信号或者复位信号的下降沿作为敏感信号,只要其中发生变化,就执行always里面的内容

if(Rst_n==1'b0)//开发板子上按键默认情况下是高电平,当按键被按下之后,就变成了低电平,所以开发板的复位状态是为0的时候。

cnt<=25'd0;

else if(cnt==25'd24_999_999)

//由于记数是从0开始的

cnt<=25'd0;//如果加了25 000 000次,就置零

else

cnt<=cnt+1'b1;

//控制LED输出状态

always@(posedge Clk50M or negedge Rst_n)

if(Rst_n == 1'b0)

led<=1'b1;

else if(cnt==25'd24_999_999)

led<=~led;//按位取反

else

led<=led;//保持当前的值,这一句不写也可以

endmodule

接下来创建counter_tb.v

`timescale 1ns/1ns

`define clock_period 20

module counter_tb;//端口例化

reg clk;

reg rst_n;

wire led;

counter counter0(

.Clk50M(clk),

.Rst_n(rst_n),

.led(led)

);

//对激励信号源进行激励的输出

initial clk = 1;

always #(`clock_period/2) clk=~clk;//每10ns翻转一次

//#代表延时

initial begin

rst_n=1'b0;

#(`clock_period*200)//200个时钟周期

rst_n=1'b1;

#2_000_000_000;

$stop;//延时2秒之后停止仿真

end

endmodule

点击assignments-setting

选择compile test bench

添加counter_tb.v文件,点击add,然后一路点击ok。

点击tools-run simulation tools-rtl simulation

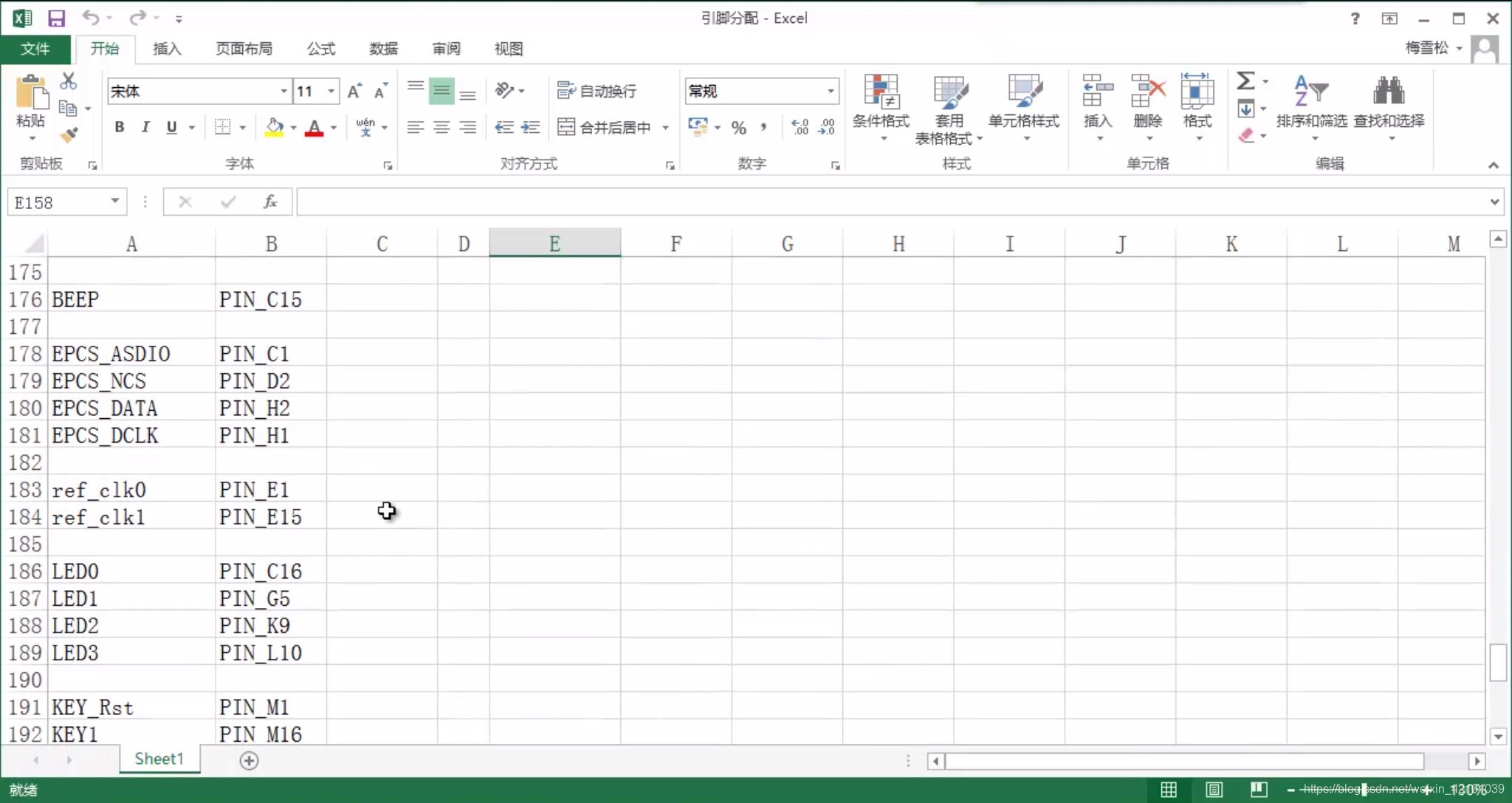

接下来是IO口的分配

点击pin planner

FPGA初学小白,如果有不对的地方请大佬们指正~

来源:CSDN

作者:居一龙的小可爱啊

链接:https://blog.csdn.net/weixin_42101039/article/details/104121912