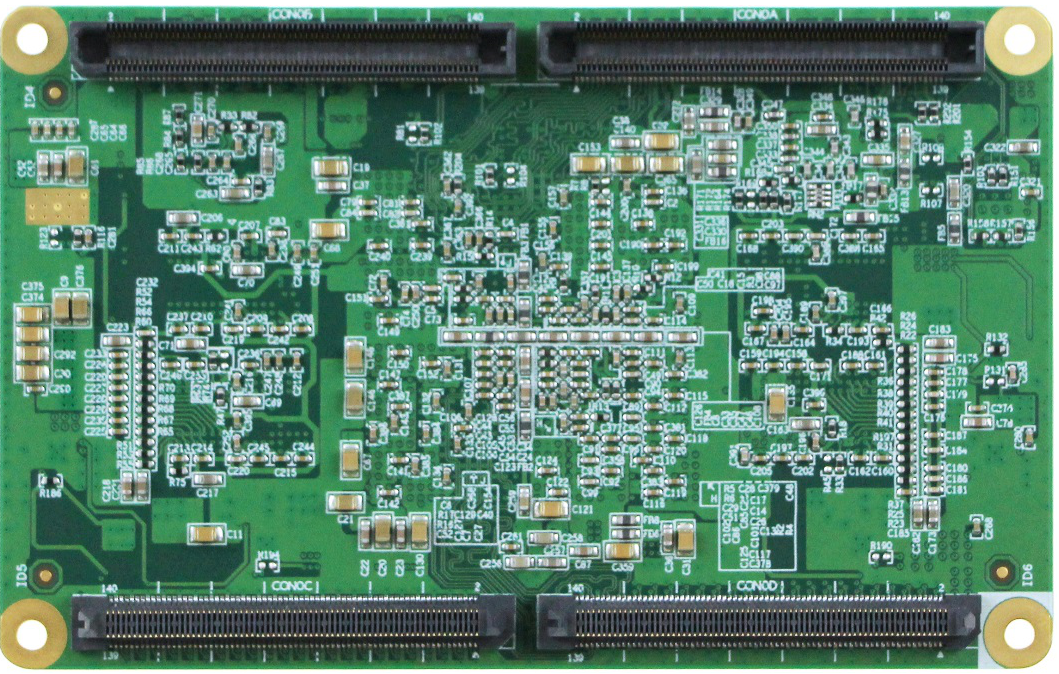

由创龙自主研发的SOM-TLZ7xH核心板,基于Xilinx Zynq-7000系列SoC高性能处理器,大小仅有100mm*62mm。采用沉金无铅工艺的14层板设计,专业的PCB Layout保证信号完整性的同时,经过严格的质量控制,非常适用于高速数据采集与处理。

SOM-TLZ7xH引出丰富的资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

基于创龙提供的丰富Demo程序,用户可同时实现硬件编程和软件编程功能,创龙将协助客户进行底板设计和调试开发。

核心板简介

基于Xilinx Zynq-7000系列SoC高性能处理器,集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源;

pin to pin兼容XC7Z035/XC7Z045/XC7Z100-2FFG900I;NOR FLASH容量为256Mbit;eMMC容量4/8GByte可选;PS与PL分别支持单通道32bit DDR总线(2x 16bit DDR);

PS端主频最高可达1GHz,单核运算能力高达2.5 DMIPS/MHz,内部集成8通道DMA控制器,通过外部存储接口可连接各种存储设备;

PL端拥有275K/350K/444K支持PS端配置的可编程逻辑单元,拥有17.6/19.2/26.5Mbit Block RAM,具备16对GTX高速串行收发器,每通道通信速率高达12.5Gbit/s;

PL端引出121pin单端IO,80对通用差分对,40对GTX专用差分对(8对为时钟),可在底板连接FMC、SFP+、PCIe等高速接口,实现功能拓展;

PS端拥有多达54个MIO引脚,也可驱动EMIO控制PL端最多64个GPIO引脚,灵活配置各种外设接口;

内部集成两路12bit ADC模数转换器,1MSPS转换率,17个差分输入通道,满足广泛模拟数据采集和监控需求;

核心板内部集成USB PHY、Ethernet PHY芯片,直接引出1路USB 2.0、1路千兆以太网信号;

可通过PS端配置及烧写PL端程序,且PS端和PL端可以独立开发,同时具备了硬件编程和软件编程功能;

核心板大小100mm*62mm,采用工业级精密B2B高速连接器,0.5mm间距,防反插,连接稳定,保证型号完整性;

提供SoC综合开发、Baremetal裸机开发、FREERTOS实时操作系统、HDL/HLS开发等例程,支持SoC一体化开发。

典型运用领域

工业电机控制

医疗设备

雷达声纳

LTE无线电和基带

电力采集

机器视觉

开发资料

提供核心板引脚定义、可编辑底板原理图、可编辑底板PCB、芯片Datasheet,缩短硬件设计周期;

提供系统烧写镜像、内核驱动源码,以及丰富的Demo程序;

提供完整的平台开发包、入门教程,节省软件整理时间,上手容易;

提供详细的SoC综合开发教程,解决一体化开发瓶颈。

汽车驾驶员辅助

来源:oschina

链接:https://my.oschina.net/u/4169033/blog/3114753