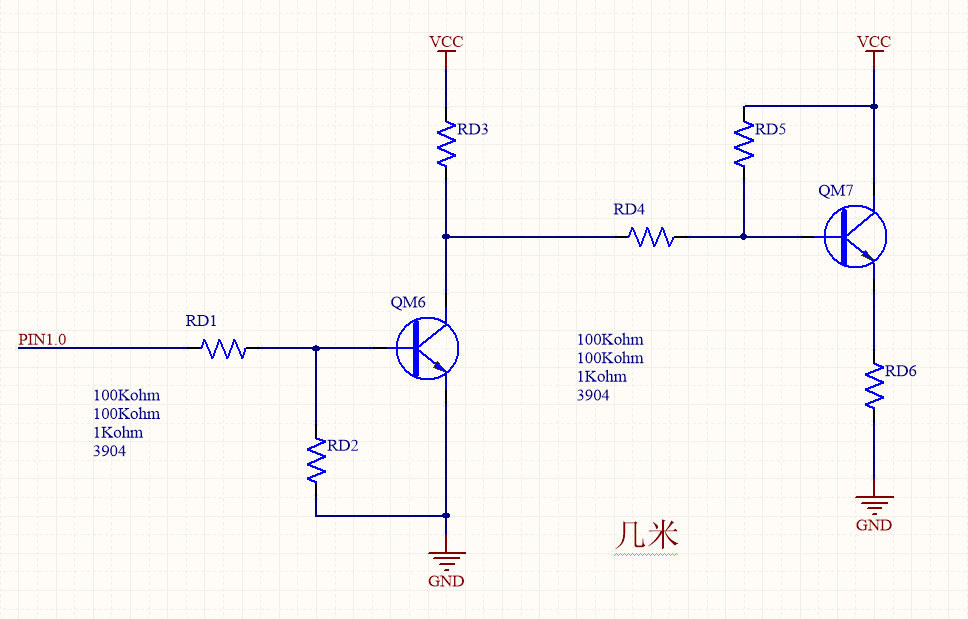

1.基极必须串接电阻,保护基极,保护CPU的IO口。

2.基极根据PNP或者NPN管子加上拉电阻或者下拉电阻。

3.集电极电阻阻值根据驱动电流实际情况调整。同样基极电阻也可以根据实际情况调整。

基极和发射极需要串接电阻,该电阻的作用是在输入呈高阻态时使晶体管可靠截止,极小值是在前级驱动使晶体管饱和时与基极限流电阻分压后能够满足晶体管的临界饱和,

实际选择时会大大高于这个极小值,通常外接干扰越小、负载越重准许的阻值就越大,通常采用10K量级。

防止三极管受噪声信号的影响而产生误动作,使晶体管截止更可靠!三极管的基极不能出现悬空,当输入信号不确定时(如输入信号为高阻态时),加下拉电阻,就能使有效接地。

特别是GPIO连接此基极的时候,一般在GPIO所在IC刚刚上电初始化的时候,此GPIO的内部也处于一种上电状态,很不稳定,容易产生噪声,引起误动作!加此电阻,可消除此

影响(如果出现一尖脉冲电平,由于时间比较短,所以这个电压很容易被电阻拉低;如果高电平的时间比较长,那就不能拉低了,也就是正常高电平时没有影响)!

但是电阻不能过小,影响泄漏电流!(过小则会有较大的电流由电阻流入地)

当三极管开关作用时,ON和OFF时间越短越好,为了防止在OFF时,因晶体管中的残留电荷引起的时间滞后,在B,E之间加一个R起到放电作用。

来源:https://www.cnblogs.com/zhangjincheng/p/4365677.html